السمعة:

- إنضم6 مارس 2024

- المشاركات 115

- الحلول 4

- مستوى التفاعل 221

- النقاط 43

بسم الله الرحمن الرحيم الحمد لله رب العالمين

بسم الله الرحمن الرحيم الحمد لله رب العالمين

والصلاة والسلام على أشرف المرسلين

تحدد بنية مجموعة التعليمات (ISA) بناء الجملة ودلالات لغة التجميع في كل بنية إنها مش مجرد بنية مختلفة ولكنها مدمجة في التصميم الأساسي للمعالج لأنها تؤثر على طريقة تنفيذ التعليمات وترتيبها ومستوى تعقيدها. يتكون ISA بشكل رئيسي من المكونات التالية:

- Instructions

- Registers

- Memory Addresses

- Data Types

Component | Description | Example |

Instructions | التعليمة اللي هتتنفذ بتكون مكتوبة في شكل opcode operand_list وبيكون فيها عادة 1 أو 2 أو 3 معاملات مفصولة بفواصل | add rax, 1, mov rsp, rax, push rax |

Registers | بتستخدم عشان تخزن المعاملات أو العناوين أو التعليمات بشكل مؤقت | rax, rsp, rip |

Memory Addresses | العنوان اللي بيتخزن فيه الداتا أو التعليمات وممكن يشير للذاكرة أو للسجلات | 0xffffffffaa8a25ff, 0x44d0, $rax |

Data Types | نوع الداتا المخزنة | byte, word, double word |

دي هي المكونات الأساسية اللي بتفرق بين ISA المختلفة ولغات التجميع هنغطي كل واحد فيهم بالتفصيل في الأقسام الجاية وهنتعلم إزاي نستخدم تعليمات متنوعة

فيه نوعين رئيسيين من بنية مجموعة التعليمات مستخدمين على نطاق واسع:

معمارية مجموعة التعليمات المعقدة (CISC) - مستخدمة في معالجات إنتل وأيه إم دي في معظم الكمبيوترات والسيرفرات

معمارية مجموعة التعليمات المنقحة (RISC) - مستخدمة في معالجات ARM وأبل في معظم الهواتف الذكية وبعض اللابتوبات الحديثة

يلا نشوف المميزات والعيوب لكل واحدة والاختلافات الرئيسية بينهم

CISC

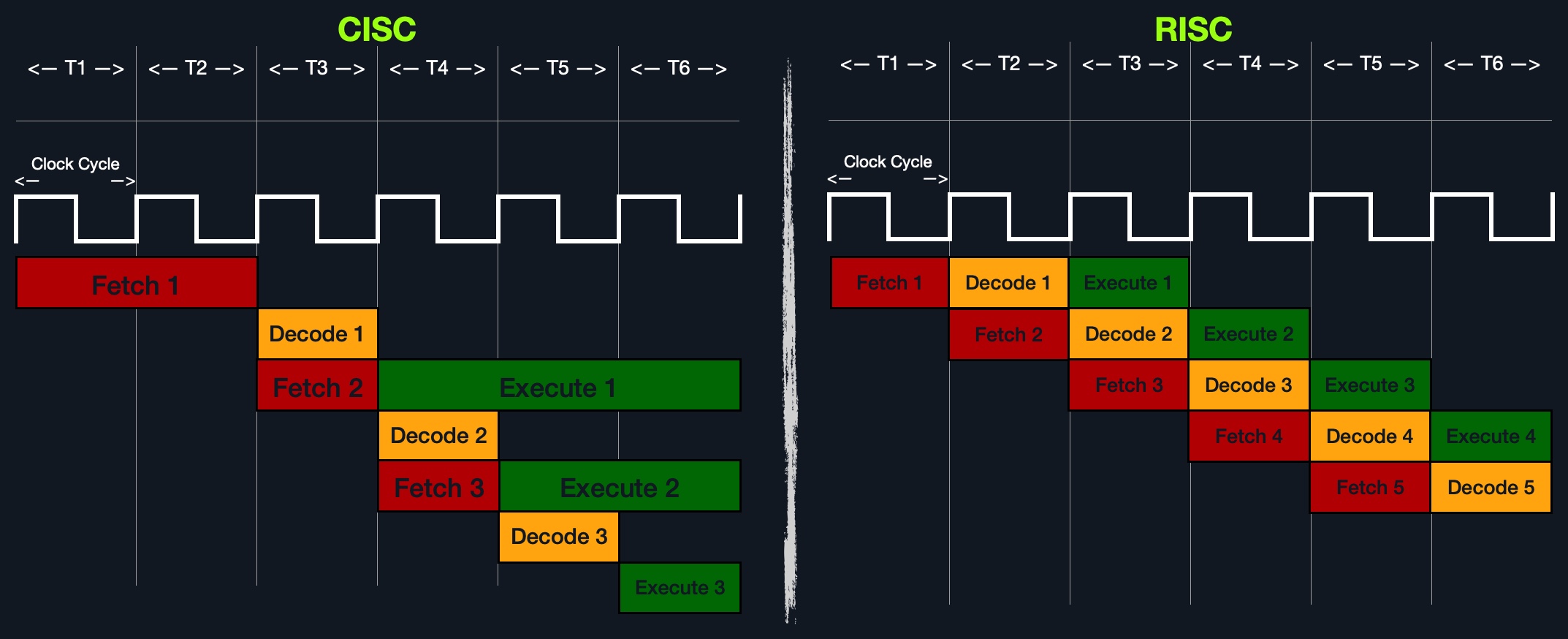

بنية CISC كانت واحدة من أولى بنى مجموعة التعليمات اللي اتطورت ومعناها إنها بتفضل التعليمات المعقدة اللي تشتغل مرة واحدة عشان تقلل عدد التعليمات الكلي اللي لازم تتنفذ وهي مصممة عشان تعتمد على المعالج بأقصى شكل ممكن عن طريق دمج التعليمات البسيطة في تعليمات معقدةمثلاً لو عايزين نجمع سجلين مع بعض باستخدام التعليمة add rax rbx المعالج اللي بيشتغل بنظام CISC يقدر ينفذ ده في دورة واحدة من Fetch-Decode-Execute-Store من غير ما يحتاج يقسم العملية لتعليمات متعددة عشان يجيب rax بعدين يجيب rbx بعدين يجمعهم وبعدين يخزن النتيجة في rax وكل واحدة من دول كانت هتحتاج دورة خاصة بيها

في سببين رئيسيين خلو التصميم ده شائع

عشان يقدر ينفذ تعليمات أكتر في نفس الوقت عن طريق تصميم المعالج ينفذ تعليمات أكثر تعقيداً في قلبهفي الماضي كانت الذاكرة والترانزستورات محدودة فكان الافضل كتابة برامج قصيرة عن طريق دمج تعليمات متعددة في واحدةلكن عشان المعالج ينفذ التعليمات المعقدة تصميم المعالج بيكون معقد برضو لأنه لازم ينفذ كمية كبيرة من التعليمات المختلفة وكل واحدة منهم لها وحدة تنفيذ خاصة بيها

وكمان رغم إن تنفيذ التعليمات المعقدة ممكن يتم في دورة واحدة إلا إن كل دورة بتنفيذ التعليمات المعقدة بتاخد وقت أكتر عشان التعليمات بتكون أكثر تعقيد فده بيؤدي لاستهلاك طاقة أكتر وحرارة أكتر عشان يتم تنفيذ كل تعليمة

RISC

بنية RISC بتفضل تقسيم التعليمات لتعليمات بسيطة عشان المعالج يتصمم يتعامل مع التعليمات السهلة بس وده بيساعد في تحسين البرمجيات عن طريق كتابة كود تجميع مُحسن قدر الإمكانمثلاً لو خدنا نفس التعليمة على معالج RISC هيتطلب إنه يجيب r2 الأول بعدين يجيب r3 بعدين يجمعهم وبعدين يخزن النتيجة في r1 وكل تعليمة من دول بتاخد دورة كاملة من Fetch-Decode-Execute-Store وده معناه إنه هيكون عندنا عدد أكبر من التعليمات الكلية في البرنامج وبالتالي كود التجميع هيبقى أطول

بما إن المعالجات RISC مش بتدعم أنواع معقدة من التعليمات فهي تدعم عدد محدود من التعليمات حوالي 200 مقارنةً بالمعالجات CISC اللي تدعم حوالي 1500 تعليمة عشان ننفذ التعليمات المعقدة بنحتاج نستخدم مجموعة من التعليمات البسيطة عن طريق كود التجميع

والمثير إنه ممكن نبني كمبيوتر عام باستخدام معالج يدعم تعليمة واحدة بس! وده معناه إننا ممكن نخلق تعليمات معقدة جداً باستخدام تعليمة sub بس تقدر تفكر في كيفية تحقيق ده

من ناحية تانية، ميزة تقسيم التعليمات المعقدة لتعليمات بسيطة هي إن كل التعليمات بتكون بنفس الطول سواء كانت 32-bit أو 64-bit وده بيساعد في تصميم سرعة ساعة المعالج عشان كل مرحلة في دورة التعليمات تاخد بالضبط دورة ساعة واحدة

الرسم البياني اللي تحت بيوضح إزاي تعليمات CISC بتاخد عدد متغير من دورات الساعة بينما تعليمات RISC بتاخد عدد ثابت من دورات الساعة :

تنفيذ كل مرحلة من مراحل التعليمات في دورة ساعة واحدة وتنفيذ تعليمات بسيطة بس بيخلي معالجات RISC تستهلك جزء صغير من الطاقة مقارنةً بمعالجات CISC وده بيخلي المعالجات دي مثالية للأجهزة اللي بتشتغل على البطاريات زي الهواتف واللابتوبات .

التعديل الأخير بواسطة المشرف: